As semiconductor technology continues to evolve, power efficiency has become one of the most important design goals in modern integrated circuits. Advanced chips such as mobile processors, AI accelerators, and IoT controllers rely heavily on low-power techniques to reduce energy consumption and extend battery life.

One of the most widely used techniques for saving power is power gating, where certain blocks of a chip are turned off when they are not needed. However, shutting down parts of a circuit creates a new challenge. Signals coming from the powered-down block may become undefined and can interfere with other active parts of the chip.

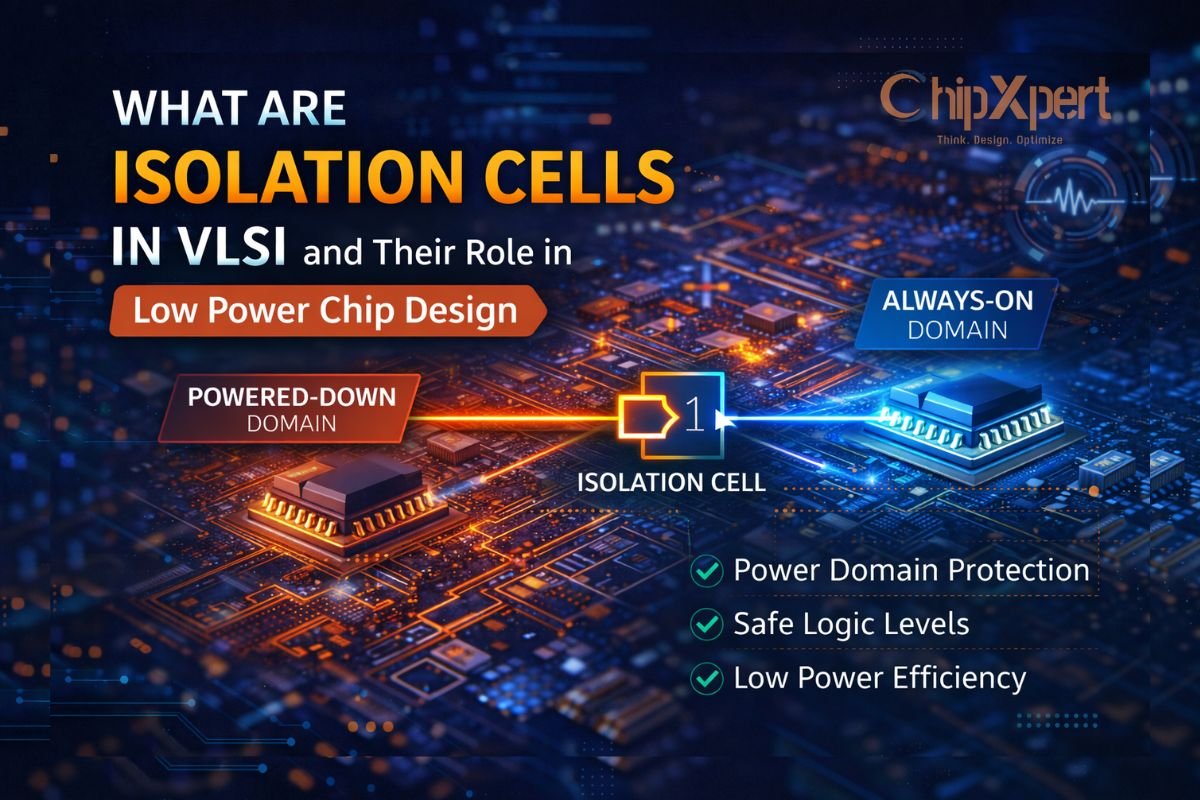

To solve this problem, designers use isolation cells. These special cells ensure that signals from inactive power domains do not disturb the rest of the system.

Understanding Isolation Cells in VLSI

Isolation cells are special logic elements placed between two power domains in a chip. Their main purpose is to prevent invalid signals from propagating when a particular block of the circuit is powered off.

When a power domain is active, the isolation cell allows signals to pass normally. However, when the domain is turned off, the isolation cell forces the output signal to a predefined logic value such as logic 0 or logic 1.

By doing this, the rest of the chip continues to receive stable and predictable signals even when certain blocks are inactive.

Why Isolation Cells Are Important

Modern system-on-chip designs often contain multiple power domains. Some domains operate continuously, while others are dynamically turned on or off to save power.

When a domain is powered down, the transistors inside that block stop functioning correctly. The outputs of that block can float or produce unpredictable values. If those outputs feed into other active logic blocks, they may cause incorrect operations.

Isolation cells prevent these issues by blocking unstable signals and maintaining safe output levels. This makes them essential for maintaining system stability in multi-power domain designs.

How Isolation Cells Work

An isolation cell acts like a controlled logic gate. It is placed between the output of a power-gated domain and the input of an active domain.

The behavior of the isolation cell depends on a control signal that indicates whether the domain is active or powered down.

When the domain is active

the isolation cell behaves like a buffer and passes signals normally.

When the domain is powered down

the isolation cell clamps the output to a fixed logic value.

This ensures that downstream logic receives a known signal instead of unpredictable data.

Types of Isolation Cells

Isolation cells are typically implemented in two common configurations depending on the required logic value during power shutdown.

Clamp-to-Zero Isolation Cell

In this configuration, the output is forced to logic 0 when isolation is enabled. This type is commonly implemented using logic structures similar to an AND gate.

Clamp-to-One Isolation Cell

In this case, the output is forced to logic 1 during isolation. It is usually implemented using logic similar to an OR gate.

The choice between these two types depends on the design requirements and the logic expectations of the receiving circuitry.

Placement of Isolation Cells in Chip Design

Isolation cells are placed at the boundaries where signals cross between different power domains. Specifically, they are inserted between a power-gated block and an always-on block.

By placing isolation cells at these boundaries, designers ensure that unstable signals from powered-down circuits never reach active parts of the chip.

Modern design tools can automatically insert isolation cells during synthesis based on the defined power architecture.

Isolation Cells in Low Power Design Architecture

Isolation cells are only one part of the broader low power design strategy used in modern semiconductor systems.

Other components commonly used in power-aware design include:

- Level shifters for voltage domain crossings

- Retention registers for preserving data during shutdown

- Power switch cells for controlling power gating

Together, these components enable designers to build energy-efficient chips that can dynamically manage power without affecting functionality.

Challenges When Using Isolation Cells

Although isolation cells are essential for reliable low-power operation, they introduce a few design considerations.

Timing Impact

Since isolation cells sit in signal paths, they can add small delays that must be considered during timing analysis.

Area Overhead

Additional cells increase the overall cell count in the design, which may slightly affect chip area.

Control Signal Coordination

Isolation control signals must be carefully synchronized with power gating signals to avoid functional errors during power transitions.

Proper design planning and verification tools help engineers manage these challenges effectively.

Isolation Cells in Modern Advanced Nodes

As semiconductor nodes shrink and chip complexity increases, multi-power domain architectures are becoming more common. This makes isolation cells even more critical.

In advanced designs, isolation logic helps ensure reliable operation when different parts of the chip enter sleep modes, standby states, or dynamic power saving conditions.

Without isolation cells, many low power techniques would introduce instability into the design.

Conclusion

Isolation cells are an essential component of modern VLSI low power design. They protect active parts of a chip from undefined signals generated by power-gated blocks. By clamping signals to safe logic levels, isolation cells help maintain reliable communication between power domains.

As chip architectures continue to grow more complex and power management becomes increasingly important, isolation cells will remain a critical part of successful semiconductor design.

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.