In the world of VLSI (Very-Large-Scale Integration) design, timing is everything. Ensuring that a chip meets its performance targets requires precise analysis of signal paths, but not all paths are equally important. This is where the concept of a false path comes into play.

For engineers and students preparing for roles in digital design and verification, understanding false paths is essential. They directly impact timing analysis, optimization strategies, and final performance outcomes.

In this article, we’ll break down false paths in an intuitive way, what they are, why they matter, and how they are used in real-world designs.

What Is a False Path?

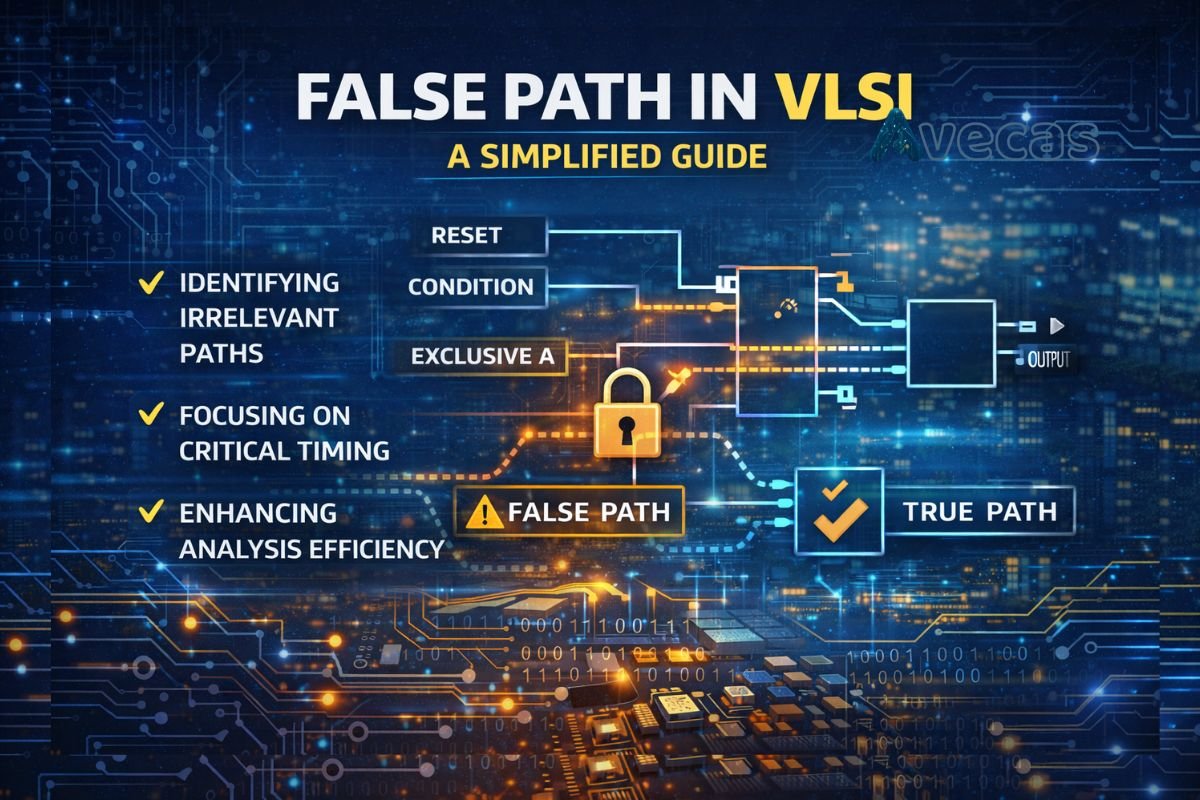

At its core, a false path refers to a timing path within a digital design that never affects the actual operation of a circuit. In other words, even if the path takes a long time to propagate signals, it doesn’t constrain or limit performance because the logic never activates that path during normal operation.

Imagine a street in a city that never gets any traffic, even if the road is long or slow, it doesn’t affect how fast cars can travel overall because vehicles never use that route. Similarly, a false path doesn’t dictate the maximum frequency a chip can run at.

Identifying false paths helps designers avoid wasting time fixing timing issues that don’t matter.

Why False Paths Matter in Timing Analysis

In static timing analysis (STA), every possible signal path between registers or timing endpoints is evaluated to ensure that data arrives on time. However, this exhaustive analysis includes paths that are functionally irrelevant.

Without marking false paths, timing tools may report violations that are technically true, yet functionally meaningless. This can:

- Mislead designers into chasing non-issues

- Increase verification time

- Lead to unnecessary design changes

By recognizing and specifying false paths, engineers can focus on the actual constraints that impact performance.

How False Paths Occur

False paths typically arise due to design logic conditions that prevent certain transitions from ever happening. Some common scenarios include:

1. Mutually Exclusive Control Signals

When the logic ensures that two signals can never be active simultaneously, any path depending on both may never be activated.

2. One-Time Initialization or Reset Paths

Paths that are only active during reset or initialization and not during functional operation are often false with respect to normal timing requirements.

3. Condition-Dependent Logic Blocks

If a path is controlled by conditions that never occur during real operation, that path doesn’t affect performance.

Understanding these conditions allows designers to characterize paths more accurately.

How False Paths Are Identified

Identification of false paths requires both functional insight and timing analysis tools:

Functional Insight

Designers must know which parts of logic are activated in typical use cases and which are not. Documentation, simulations, and design intent help in this stage.

Timing Tools

Static timing analysis tools allow annotations or constraints that specify false paths. These annotations communicate to the timing engine that certain paths need not be considered for timing closure.

Together, design knowledge and tool support help refine timing analysis.

Benefits of Using False Path Analysis

Incorporating false path identification into the VLSI design flow offers several advantages:

Improved Timing Closure

By excluding irrelevant paths, timing engines can focus on the true critical paths, helping designers meet performance targets more efficiently.

Reduced Verification Effort

Eliminating meaningless violations saves time and effort in debugging and optimization.

Better Design Optimization

With clearer insight into which paths matter, designers can apply targeted optimization techniques like buffering, restructuring logic, or retiming only where it truly counts.

The result is a faster, more efficient design process with fewer iterations.

False Paths vs. Multi-Cycle Paths

Another concept often discussed with false paths is the multi-cycle path (MCP). While both involve timing exceptions, they are different:

- Multi-Cycle Paths: Paths that need more than one clock cycle to propagate data and are valid functional paths, just slower by design.

- False Paths: Paths that never affect real functional behavior.

Confusing the two can lead to incorrect timing constraints. Understanding the distinction helps in applying the right analysis techniques.

Practical Examples

To see how false paths work in practice:

Mutually Exclusive Control

Consider a logic block that triggers only when a control signal is high. If another section of the circuit only activates when that signal is low, the path between them may never be functionally exercised — hence a false path.

Reset or Initialization Blocks

Reset logic often sets initial states for registers. Timing across this path is not relevant to normal operation and can be treated as false for timing closure.

By analyzing how signals interact under real workloads, designers can identify such situations.

Best Practices for Applying False Path Constraints

Here are some guidelines when working with false paths:

1. Validate Functional Conditions

Before marking a path as false, ensure that no future use cases could activate it under valid conditions.

2. Use Precise Constraints

Generic or overly broad false path definitions can mask real timing issues. Be specific and deliberate.

3. Collaborate With Verification Teams

Functional verification teams often have insights into real operational conditions. Working together reduces risk.

These practices help maintain both performance reliability and timing accuracy.

Conclusion: False Paths Simplify Timing, Not Complexity

Understanding false paths is instrumental in mastering VLSI timing analysis. They help engineers differentiate between performance-critical paths and irrelevant ones, allowing for focused optimization and reduced design cycles.

By combining design insight with effective timing tools, false paths become a strategic advantage rather than a challenge. In the world of high-performance digital design, this clarity enables faster timing closure and more reliable chips.

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.