CMOS or Complementary Metal-Oxide Semiconductor technology is the foundation of modern digital circuits. From microprocessors to memory chips and low power IoT devices, CMOS has become the preferred technology for designers. One of the most important aspects of CMOS design is power dissipation. Reducing power dissipation helps extend battery life, improve performance, and reduce heat.

This article explains what power dissipation is, why it happens, and how designers reduce it in CMOS circuits.

What Is Power Dissipation

Power dissipation in CMOS circuits refers to the energy lost as heat or consumed by a chip while operating. Every time a circuit switches or draws current, some energy is used. In portable and battery powered devices this becomes especially critical because power directly affects battery life.

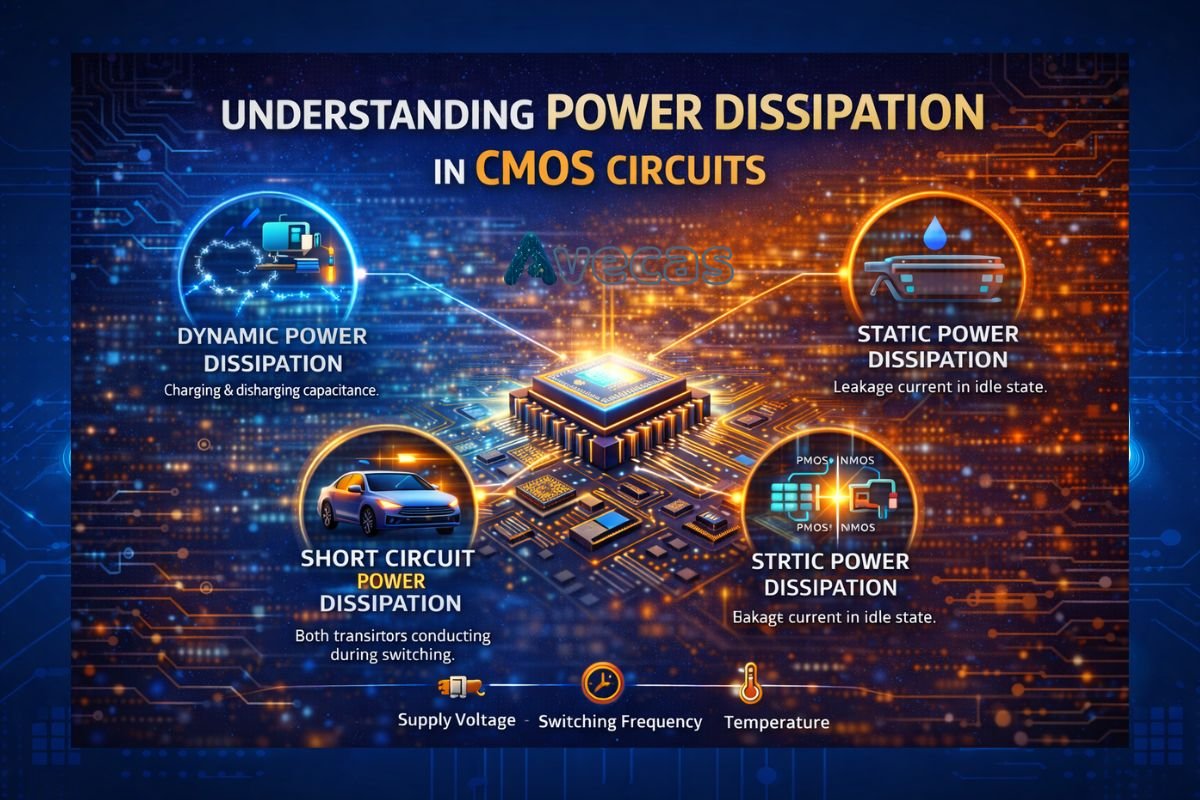

In CMOS circuits, power dissipation can be categorized into different types based on how energy is consumed while the device is active or idle.

Types of Power Dissipation in CMOS

There are three main components of power dissipation in CMOS circuits. Designers analyze each component carefully to optimize overall power consumption.

Static Power Dissipation

Static power is consumed when the circuit is not switching but is powered on. In an ideal CMOS gate, no current should flow in a steady state because complementary transistors block current paths. However in real circuits tiny leakage currents flow due to imperfections in transistors, especially as transistor sizes shrink.

As technology scales down, leakage has become a major contributor to static power. Designers use special techniques to reduce leakage such as power gating or using high threshold transistors in idle parts of a design.

Dynamic Power Dissipation

Dynamic power is the most commonly discussed type of power in CMOS circuits. It arises from charging and discharging of load capacitances when the circuit switches from one logic state to another.

Whenever a CMOS inverter switches from low to high or high to low, capacitive loads receive charges or release energy. The energy used in this process adds up quickly in circuits with frequent switching.

The dynamic power can be approximated by a simple relation that depends on capacitance, supply voltage, and switching activity. This means that higher clock speeds and larger capacitances result in higher power dissipation.

Short Circuit Power Dissipation

During switching, for short periods both NMOS and PMOS transistors in a CMOS gate may conduct simultaneously. This creates a direct current path from supply to ground, causing short circuit power dissipation. Although short circuit power is usually smaller than dynamic power it still contributes to overall energy use especially at high frequencies.

Factors Affecting Power Dissipation

Several factors influence how much power a CMOS circuit consumes during operation.

Supply Voltage

The supply voltage plays a major role in power consumption. Since dynamic power has a quadratic relationship with supply voltage even a small reduction in voltage can lead to significant power savings. This is why many systems operate at the lowest possible voltage that still meets performance requirements.

Switching Frequency

When a circuit switches more often it charges and discharges capacitance more frequently. Higher switching increases dynamic power almost linearly. Designers often reduce unnecessary switching activity to save power.

Capacitance

The load capacitance that a gate drives affects the amount of charge required per transition. Larger load capacitances lead to greater energy usage. Designers reduce capacitance through careful layout and by minimizing long interconnects.

Temperature

As temperature rises, leakage currents increase. This increases static power dissipation. Good thermal management and low leakage design techniques help control power rise due to temperature.

Techniques to Reduce Power Dissipation

Reducing power consumption is a major goal in modern design. Several effective techniques have been developed to minimize power use in CMOS circuits.

Voltage Scaling

Since dynamic power depends strongly on supply voltage, lowering it is one of the most effective ways to reduce power. Many modern systems use dynamic voltage scaling where a processor adjusts its voltage based on workload.

Lowering voltage reduces energy per transition and also decreases leakage in some cases. However designers must ensure that the circuit still meets timing and performance targets.

Clock Gating

Clock signals drive switching events across a design. By shutting off the clock to parts of the circuit that are idle, designers eliminate needless switching. This technique called clock gating is widely used in processors and digital systems to reduce dynamic power.

Power Gating

Power gating involves completely cutting off power from sections of a circuit when they are not in use. Unlike clock gating power gating reduces both dynamic and static power because the circuit block no longer draws current.

Multi Threshold Design

Using a mix of high threshold and low threshold transistors helps reduce leakage. High threshold transistors are used in non critical paths to reduce leakage while low threshold transistors are used where performance is necessary.

Architectural Techniques

In addition to circuit level solutions, designers also use architectural methods such as reducing switching activity, using parallel processing efficiently, and minimizing activity in idle modules to control power usage.

Importance of Power Optimization

Efficient power management is critical in many modern applications. In battery powered devices like mobile phones, tablets and wearable systems longer battery life is a key user requirement. In high performance computing systems excess power leads to heat which negatively affects performance and reliability.

Even in large data centers power efficiency translates into lower operating cost and improved sustainability. All of these factors make power dissipation an important consideration throughout the design process.

Conclusion

Power dissipation in CMOS circuits is a fundamental design challenge that impacts performance, reliability and battery life. By understanding the different forms of power loss and applying techniques such as voltage scaling, clock gating and power gating, designers can build more efficient systems.

As technology continues to scale and circuits become more complex, power optimization remains a central part of semiconductor design. Engineers who master power dissipation concepts are better equipped to create high performance and energy efficient chips for the next generation of technology.

Share your question in comments or talk to our mentor team for batch guidance.

Ask the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.