In VLSI design, digital signals are expected to represent clear logic levels, either a logic high or logic low. However, real circuits are not perfect. Voltage levels can vary due to power supply noise, temperature shifts, crosstalk, and other electrical interference. This makes it essential to understand noise margin, a key concept that ensures reliable digital operation even in the presence of unwanted disturbances.

This article explains what noise margin is, how it is measured, and why it plays a crucial role in designing robust VLSI systems. Whether you are a student beginning your journey in digital design or an engineer optimizing chip performance, understanding noise margin is essential.

What Is Noise Margin

Noise margin refers to the range of voltage within which a digital circuit can tolerate unwanted disturbances without misinterpreting the logic level. In simpler terms, it is the buffer area between the actual signal and the threshold where a logic high or logic low is recognized correctly.

Since digital systems are built on discrete voltage levels, these levels must be distinct enough that noise does not cause false switching. Noise margin quantifies how much noise a system can handle before it fails to interpret a logic state correctly.

Logic Levels and Their Thresholds

In most digital circuits, two voltage ranges represent logic states:

- Logic high (1) is represented by a voltage near the supply voltage.

- Logic low (0) is represented by a voltage near ground.

Each logic level has an acceptable voltage range that ensures the correct interpretation of the signal. These ranges are defined by the input and output characteristics of digital gates.

When a gate outputs a logic high, the receiving gate must recognize it as a valid high even if noise reduces its voltage slightly. Similarly, a logic low must remain low enough despite noise that could increase its level slightly.

Noise margin sets the minimum deviation the circuit can tolerate without causing errors.

Noise Margin in Digital Circuits

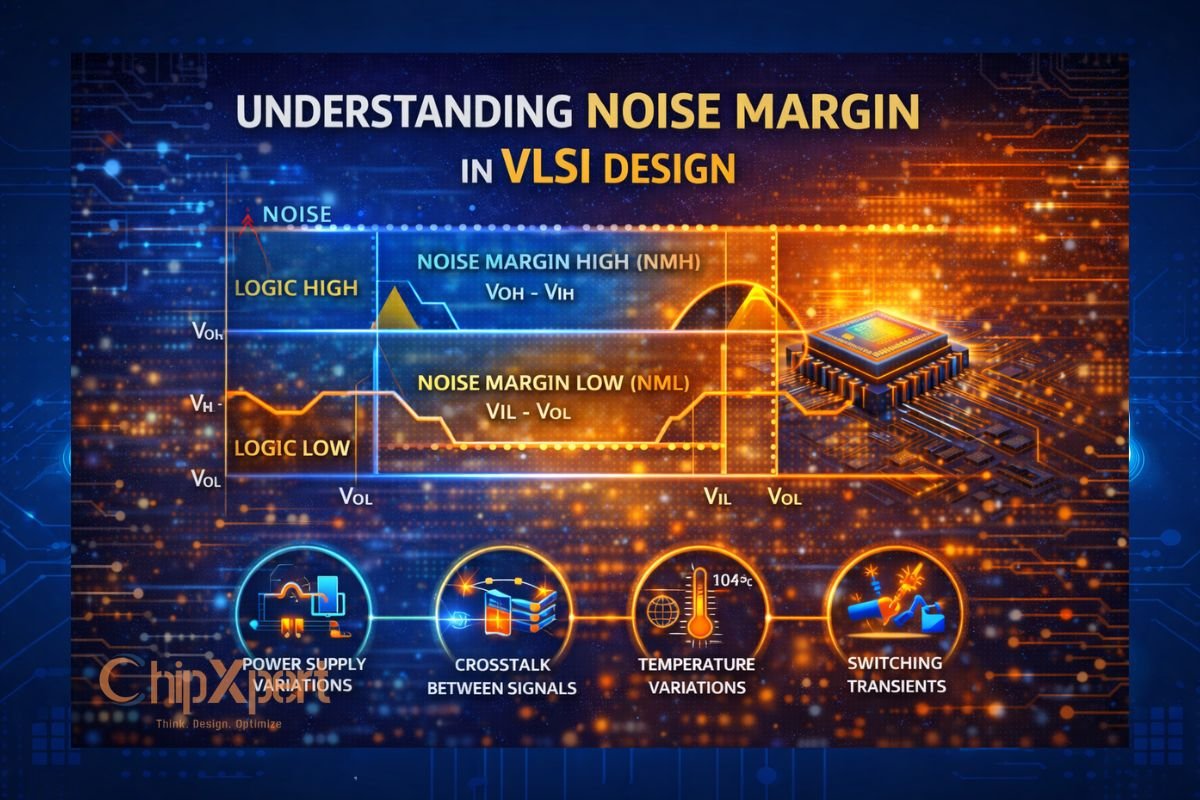

To better understand noise margin, consider the following conceptual values:

- VOH is the minimum voltage that an output can produce while still being recognized as a logic high.

- VIH is the minimum voltage the input must receive to treat the signal as logic high.

- VOL is the maximum voltage that an output can produce and still be considered a logic low.

- VIL is the maximum voltage the input will accept and still recognize the signal as logic low.

The differences between these values determine the noise margins for high and low states:

- Noise Margin High (NMH) is the difference between VOH and VIH.

- Noise Margin Low (NML) is the difference between VIL and VOL.

In practical design, larger noise margins mean the circuit is more tolerant to variations and disturbances.

Why Noise Margin Is Important in VLSI Design

As circuits become more complex, smaller in size, and operate at higher speeds, noise becomes a bigger challenge. Several factors influence noise behavior:

Power Supply Variations

Fluctuations in supply voltage can shift logic levels. If a circuit has poor noise margin, a small change in supply voltage might cause a logic high to be misinterpreted as a logic low.

Crosstalk Between Signals

In dense chip layouts, signals running near other signals can induce interference that affects voltage levels. High noise margin helps ensure that signals remain classified correctly even when they influence each other.

Temperature and Process Variations

Semiconductor behavior changes with temperature and manufacturing process differences. These changes can impact the voltage at which logic levels are recognized, making noise margin critical for reliable circuit behavior.

Switching Transients

When digital signals change state, brief spikes or dips in voltage can occur. Noise margin determines whether the circuit ignores these brief disturbances or misreads them as errors.

Designing for Better Noise Margin

Ensuring a good noise margin requires both circuit and layout strategies:

Choose Appropriate Logic Families

Different logic families have varying inherent noise margins. Designers may choose logic families with higher noise margins for applications that demand high reliability.

Control Supply Integrity

Good decoupling, proper power routing, and stable power supply design help minimize supply noise and improve overall noise tolerance.

Reduce Crosstalk

Carefully planning signal routing and shielding high-speed or sensitive lines reduces interference that erodes noise margin.

Robust Threshold Selection

By choosing logic threshold values that have sufficient separation between high and low recognition limits, designers can build in extra margin for variations.

Noise Margin and Technology Scaling

As technology scales down to smaller nodes, voltage levels also drop to reduce power consumption. Lower voltage swings make noise margin smaller unless it is compensated by improved design techniques.

This creates a design tradeoff between power efficiency and noise tolerance. Modern techniques such as differential signaling, better isolation, and advanced buffer design help maintain acceptable noise margins even at low voltages.

Conclusion

Noise margin is a fundamental concept in digital and VLSI design that determines how well a circuit can tolerate unwanted disturbances. By providing a buffer between actual signal levels and logic thresholds, noise margin ensures that digital systems interpret signals correctly despite environmental and electrical challenges.

Designers must consider noise margin throughout the design, layout, and verification stages to build reliable and robust chips. With increasing circuit complexity and shrinking transistor sizes, understanding and optimizing noise margin is more important than ever.

Learn advanced VLSI courses by Industry Experts having 15+ years of experience, Premium EDA Tool Access (24X7) and with Guaranteed Placement Assistance,

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.